台积电迈向“硅光子学”领先地位

台积电正在美国大幅增加硅光子学相关的专利申请。

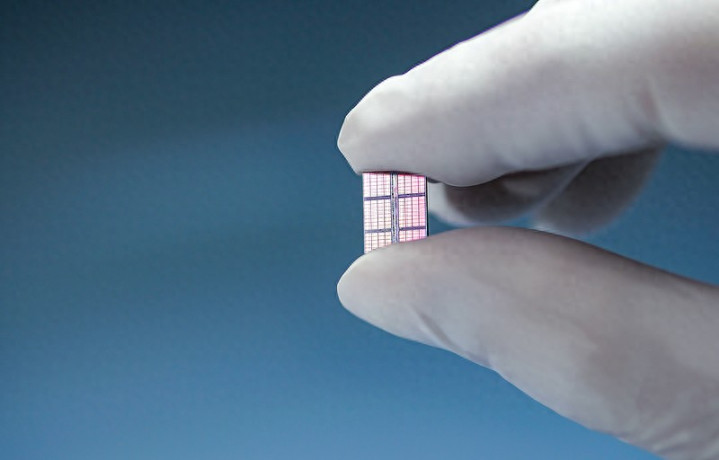

中国台湾晶圆代工企业台积电(TSMC)目前正积极在下一代人工智能(AI)芯片的核心技术 “硅光子学” 领域布局专利,力求在市场中占据领先地位,而这一举措也被视为其巩固全球第一晶圆代工企业地位的重要战略。

9 月 8 日,中国台湾《经济日报》等当地媒体援引日本的相关报道称,台积电正在美国大幅增加硅光子学相关的专利申请,今年截至目前的申请数量已经达到英特尔的两倍多,与 2023 年相比有了大幅增长 —— 要知道在 2023 年,这两家公司在该领域的专利申请数量差距还并不大。

那么,硅光子学究竟是一项怎样的技术呢?它是一种利用光而非电在半导体芯片内部传输信号的技术。电流在导线内部传输时,会因为与导线内的原子发生碰撞而减慢速度,而光则能够以每秒 30 万公里的速度进行直线传播,凭借这一特性,硅光子学技术能够实现更快、更高效的数据传输。

CPO技术涉及到光电芯片的混合集成,是当前光器件领域竞争的热点。当网络速度提高至800Gbps以上,可插拔光组件将遭遇密度和功率问题,CPO成为了业界亟需的封装替代方案。根据光通信行业市场调研公司数据显示,过去10年里全球销售的可插拔光模块达到了10亿只,其中一半用于光纤到户FTTx市场,有至少1000万只用于大型云计算公司数据中心内部互联。但是,随着数据中心用户对于功耗与高密度安装越来越高,可插拔模块渐渐不能满足需求,将在2027年-2028年开始出现向下的趋势。

在2026年,HPC和AI集群将成为CPO光学的最大细分市场。CPO出货量以800G和1.6T端口计算,可以组合成3.2T或6.4T光学芯片,采用硅光子实现 I/O 的第一步,可以轻松突破现有带宽的瓶颈,基于分解计算和存储的下一代架构再增加10倍带宽,并且在核心交换设备接口方面已经有规模化的应用。

台积电计划将硅光子学技术应用到先进封装工艺中,从而推动 “共封装光学器件(CPO)” 的商业化进程。业界对此预期,该技术还有望应用在英伟达计划于明年发布的下一代图形处理器(GPU)“Rubin” 上,进而助力这款产品实现性能的提升。

实际上,台积电和三星电子等全球范围内的代工企业,一直都在致力于基于硅光子学技术的 CPO 商业化研发。这背后的原因在于,英伟达等客户正快速提高其未来 AI 芯片所需的数据传输量和速度,而开发基于硅光子的 CPO 被普遍认为是实现这一目标的关键所在。

台积电近期对硅光子学这项技术的坚定投入,已经引起了业界的广泛关注。除了进行大规模投资外,该公司还在今年 4 月于加州圣克拉拉举行的 “北美技术论坛” 上,公布了将硅光子技术融入各种制造工艺的愿景。具体来说,台积电宣布今年已经完成了 “COUPE”(即把电子芯片堆叠在光子芯片上)的验证工作,并计划在明年将硅光子技术应用到其先进的封装技术 “晶圆基板芯片封装(CoWoS)” 中,以此来打造 “共封装光学元件”。此外,台积电还在与专注于专用集成电路(ASIC)和高速网络芯片的美国公司 Marvell Technology 展开合作,目的是应对不断扩张的硅光子市场,同时开发适用于 3 纳米(1 纳米等于十亿分之一米)及以下工艺的下一代硅光子技术。

CPO技术为大型数据中心运营商在可插拔模块之外提供了新的选择。在未来,硅光子技术演进将集中在更高集成度,先进的硅光子制造工艺和封装技术将会成为硅光子技术演进的核心技术支撑。

业界进一步预期,随着台积电硅光子技术的日渐成熟,其主要客户英伟达的下一代 AI 芯片的量产和上市进程将会得到加速。据悉,英伟达也已经决定在其计划于明年发布的 AI GPU “Rubin” 中广泛采用硅光子技术,并且会运用 CoWoS 等 2.5D 和 3D 封装技术,英伟达希望通过这样的方式,解决芯片之间电力连接所带来的瓶颈问题以及功耗过高的问题。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。

想要获取半导体产业的前沿洞见、技术速递、趋势解析,关注我们!